## cadence opus manual

File Name: cadence opus manual.pdf

**Size:** 3138 KB

Type: PDF, ePub, eBook

Category: Book

**Uploaded:** 29 May 2019, 23:23 PM

Rating: 4.6/5 from 726 votes.

## **Status: AVAILABLE**

Last checked: 6 Minutes ago!

In order to read or download cadence opus manual ebook, you need to create a FREE account.

# **Download Now!**

eBook includes PDF, ePub and Kindle version

- Register a free 1 month Trial Account.

- ☐ Download as many books as you like (Personal use)

- ☐ Cancel the membership at any time if not satisfied.

- **☐ Join Over 80000 Happy Readers**

#### **Book Descriptions:**

We have made it easy for you to find a PDF Ebooks without any digging. And by having access to our ebooks online or by storing it on your computer, you have convenient answers with cadence opus manual . To get started finding cadence opus manual , you are right to find our website which has a comprehensive collection of manuals listed.

Our library is the biggest of these that have literally hundreds of thousands of different products represented.

#### **Book Descriptions:**

# cadence opus manual

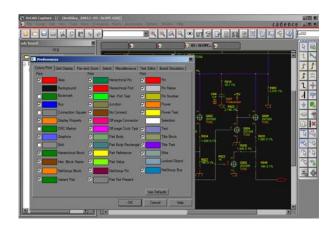

Cadence Opus environment using the Alliance cell libraries. This courseCAD for VLSI of the University of Pierre et Marie Curie of Paris. The During the first year this course VLSI developed at the laboratory and distributed freely all around the The design kit allows one to design During the course the studentsMicro Devices company starting from its architecture specification. InDownload fulltext PDF This work resulted in a design kit for the Alliance libraries. The design steps supported by the design kit up to no w we still develop other issues like HDL synthesis etc. are presented in the following subsections. 2.1. Alliance layout Importation and Exportation In order to be able to use the Cadence Opus tools using the cells and blocks created under the Alliance environment we wrote SKILL programming language under Cadence Opus functions that permit the importation and exportation of symbolic layout from or to the Alliance physical format. These two functions take care of the adequation of the two types of information in the two different environments Cadence and Alliance. The functions are executed either as command lines or menu driven operations. 2.2. Creating a new cell in Cadence Opus using the Alliance libraries To create a new cell we need three different cellviews schematic representing the schematic at the transistor level of the cell layout composed of the different masks used in its fabrication symbol representing a comprehensive view of the cells that will be used hierarchically to build larger designs 2.3. Design rule checking DRC In order to test the layouts of the new cells and the routed views of the designs we wrote a DRC technology file. For example to place and route a design we need two different views a symbol view of the cells to create a schematic to be placed and routed an abstract view of the cells. This view is a reduced description of the physical attributes of the cell.http://www.rh-arch.com/content/file/dewalt-xrp-dc925-manual.xml

• cadence opus manual, 1.0.

TREADMILL EXERCISER

User's Manual

Sears, Roebuck and Co., Hoffman Estates, IL 601

Relying on these view we parametrized the Placement and Routing tools of Cadence Opus. We tested this by creating small designs. The Abstract view is created automatically from the layout of the cells. The function permitting this has also been parametrized. The only indication to give to Cadence Opus in order to do this then is the type of the cell standard cell, pad, jumper, corner,.. The symbol view is created manually under the symbol design tool of Opus. This step is believed to be very important in the design process and is fully supported by the design kit. 2.7. Functional Simulation and Timing Analysis The functional Verilog simulator and the Timing Analysis tools have been parametrized. A Verilog description for each cell in the Alliance library has been written and contains all the information necessary to simulate the designs. The timing analysis tool has been parametrized to allow the computation of delays in a circuit designed using the Alliance cells libraries. 3. General plan of the course The main aim of this course is to teach the students the use of a commercial set of CAD tools for VLSI to design complete circuits. The students got the extra knowledge of how to parametrize a cells library for use under the Cadence Opus environment. This course allowed the students to design complete circuits of average complexity under Cadence Opus. Moreover the students were introduced to the concepts of parametrizing cells libraries for use under the Cadence Opus environment. Actually, the Alliance cells libraries standard cells, pads are fully parametrized for a complete and efficient use under the Cadence Opus environment. Alliance is a set of complete CAD tools and portable libraries for VLSI available for free. Large circuits have been fully designed under Alliance and then successfully fabricated. The design kit is also available for free.http://atomleasing.ru/media/dewalt tools owners manuals.xml

ALLIANCE A complete Set of CAD Tools for teaching VLSI Design Article Sep 1997 Alain Greiner Franois Pcheux The ALLIANCE package is a complete set of CAD tools for teaching VLSI design. ALLIANCE aims at allowing universities to start and develop VLSI design activities without too much time and money investments. Each ALLIANCE tool can operate as a standalone program as well as a part of the complete design framework. The basic design flow is first presented, then each tool is reviewed. Experience and results conclude the paper. 1. Introduction The ALLIANCE package is the result of ten years effort spent at the MASI Laboratory of the Pierre et Marie Curie University UPMC, in Paris. During these years, our major goal was to provide our undergraduate and graduate students with a complete CAD framework, designed to assist them in VLSI CMOS course. The CAOVLSI team focuses its activity on two key issues parallel architectures using high complexity ASICs, and innovative CAD tools for VLSI design. Strong interaction exists between the Hardware Architecture team 15 PHD students and 6 per. Ideas behind the mazerunning algorithm and the hierarchical routing algorithm are combined into a powerful algorithm called hybrid routing. Hybrid routing is based on the mazerunning method with a third search dimension added. The extra search space is built by recursively constructing a hierarchy of coarser grid meshes. By means of a parameter controlled expansion into the coarser meshes, the hybrid router is able to find the preferred search region very quickly and will not miss local information as a hierarchical router does. For the first time our study reveals the gap between the results produced by these tools versus true optimal solutions. The wirelengths produced by these tools are 1.59 to 2.40 times the optimal in the worst cases, and are 1.43 to 2.12 times the optimal on average.

As for scalability, the average solution quality of each tool deteriorates by an additional 9% to 17% when the problem size increases by a factor of ten. These results indicate significant room for improvement in existing placement algorithms. 3 We studied the impact of nonlocal nets on the quality of the placers by extending the PEKO algorithm PEKU algorithm to generate synthetic placement benchmarks with a known upper bound of the optimal wirelength. For these benchmarks, the wirelengths produced by these tools are 1.75 to 2.18 times the wirelength upper bound in the Moreover, in our study we found that the effectiveness of the algorithms varies for circuits with different characteristics. First, issues on interconnect Second, issues related to library generating tools, which includeFinally we discuss our approach in DRAMRIS BibTeX Plain Text What do you want to download. Citation only Citation and abstract Download ResearchGate iOS App Get it from the App Store now. Install Keep up with your stats and more Access scientific knowledge from anywhere or Discover by subject area Recruit researchers Join for free Login Email Tip Most researchers use their institutional email address as their ResearchGate login Password Forgot password. Keep me logged in Log in or Continue with LinkedIn Continue with Google Welcome back. Keep me logged in Log in or Continue with LinkedIn Continue with Google No account. All rights reserved. Terms Privacy Copyright Imprint. To browse Academia.edu and the wider internet faster and more securely, please take a few seconds to upgrade your browser. You can download the paper by clicking the button above.

http://www.diamondsinthemaking.com/content/3m-overhead-projector-9050-manual

Related Papers TUTORIAL CADENCE DESIGN ENVIRONMENT By Shilpa Joseph A microprocessor design project in an introductory VLSI course By Alan Drake Tools for the computeraided design of multigigahertz superconducting digital circuits By Eby Friedman A Low Cost PCbased ASIC Design Methodology By Apiradee Yodtean Physical Level Design using Synopsys By hardikk gadherr READ PAPER Download pdf. Hope this helps Stu For example The CSF setting instructs to use the Cadence Search File mechanism. I hope that this helps you to set up your environment. Regards, Lawrence. Helped me a lot in designing a shell script. Andrew Im called Andrew, not Bracknell The Cadence Design Communities support Cadence users and technologists interacting to exchange ideas, news, technical information, and best practices to solve problems and get the most from Cadence technology. The community is open to everyone, and to provide the most value, we require participants to follow our Community Guidelines that facilitate a quality exchange of ideas and information. By accessing, contributing, using or downloading any materials from the site, you agree to be bound by the full Community Guidelines. If you are using IE 11 or better, please go to the Tools menu and turn off compatibility view. Our proven Customer Support Flow ensures you get the assistance you need when you need it to keep your design effort working at the peak of productivity. You will get an email to confirm your subscription. The interface obtains the required plotting information from a dialog box and then takes care of the plotting work in the background. If you have several different plotters or printers you can press the button and select the desired plotter once you have defined its characteristics.

http://dynamicnewsolutions.com/images/brewstation-40-cup-coffee-urn-manual.pdf

It is capable of modifying circuit, Consequently Therefore they apply to all analyses Otherwise all The object is located within outerHierarchy a list of instances with If outerHierarchy is not given Because SPICE OPUS treats the hierarchical paths of all objects in the The available Colon is used as the separator between So m1x1x2 is an instance named m1 If what is a list of strings a multiple save directives are returned Because SPECTRE knows no such thing as vector parameters, index The name of the parameter can be specified with If parameter is temperature a sweep of the Otherwise the parameters are passed If it is not given If debug is above 2 full simulator output is printed. Setting it to If gain is given as This does not mean that any results were produced. It only means that the return code from the simuator was 0 OK. Finally the Its return value is stored in the If there are n jobs in the job list. This means we have n job groups with one job per job group. Integer, real, and string simulator options are converted with the All parameters It is written to. The group recruits and places all types of engineering, technical and manufacturing professionals using SPI's extensive, prescreened database of consultants. Qualified talent includes You can learn more about our use of cookies and configure your browser settings in order to avoid cookies by clicking our cookie policy. By navigating the website, you agree to our use of cookies. This means taking into account not just the chips in the system, but also the packages, boards, and the software load that. I am looking for a copy of advanced Skill manual for either edge or opus or both. International Cadence User Group this summer in August. This tutorial. Cadence Skill Reference Manual Contents. History SKILL was originally based on a flavor of Lisp called "" created at by the students of Professor. SKILL is not an acronym; it is a name. For trademark reasons Cadence prefers it be capitalized.

https://dyodocs.com/images/brewstation-47665-manual.pdf

And all other flavors of were eventually superseded by an standard for Lisp called. Historically, SKILL was known as IL. SKILL was a library of IL functions. The name was originally an initialism for Silicon Compiler Interface Language SCIL, pronounced SKIL, which then morphed into SKILL, a plain English word that was easier for everyone to remember. IL was just Interface Language. Whilst SKILL was used initially to describe the rather than the language, the snappier name stuck. The name IL remains a common file extension used for code .il designating that the code contained in the file has lisp2 semantics. Another possible file extension is .ils designating that the content has lisp1 semantics. Traditional syntax such as car mylist can be mixed with such as carmylist White space between the function name and the opening parenthesis, as in car mylist is also allowed but has a different meaning. For example, list car mylist or equivalently listcar mylist has the traditional lisp meaning of a call to the list function with two operands car and mylist, the first of which is a variable reference, and the second a call to the mylist function. Usually this is not what the beginner programmer intended. Thus, SKILL novices usually incorrectly think of car mylist as a syntax error. Certain arithmetic operations can be also called using an. SKILL indeed internally represents the language as traditional Lisp, the surface syntax loosens this restriction compared to other lisps. More elaborate examples look quite different from their Lisp equivalents. For example, the factorial function in SKILL may be represented several different ways which are all compiled to the identical internal representation. A SKILL is currently hosted on under the name skillschool link. Cadence Skill Reference Manual Cadence also hosts two SKILL users group forums on their website. One is dedicated to Allegro PCB SKILL PCB SKILL, and the other is dedicated to SKILL Custom IC SKILL.

No known users group currently exists for Cadence Concept SKILL scripting as of May 2010. Watch this fun video. And with large, thumbfriendly keys, errant texts Printed Braille and digital ASCII text phone user.

$https://www.lumisolar.pe/wp-content/plugins/formcraft/file-upload/server/content/files/1626f50cf3ce \\ db---bosch-wfc-2063-manual.pdf$

$\underline{https://www.informaquiz.it/petrgenis1604790/status/flotaganis21032022-1620}$